# **SRIO SERIAL BUFFER FLOW-CONTROL DEVICE**

# Advanced Datasheet 80KSBR200

# **Device Overview**

The IDT80KSBR200 is a high speed Serial Buffer (SerB) that can connect to any Serial RapidIO compliant interface. This device is built to work with any sRIO device and especially with the IDT Pre-Processing Switch (PPS), IDT70K200. The SerB performs buffering and off-loading of data as well as buffer-delay of data samples in various environments. This device primarily acts as an master in which the SerB bursts data to a programmed memory location once some criteria have been meet. This combination of storage and flexibility make it the perfect buffering solution for sRIO systems.

### **Features**

- ◆ Serial RapidIO Port

- ◆ Interface sRIO

- One four-lane (4x) link, configurable to one-lane (1x) link Port Speeds selectable: 3.125 Gbps, 2.5 Gbps, or 1.25 Gbps

- Short haul or long haul reach for each PHY speed Support 8-bit and 16-bit deviceID

- Error management supports standard

- sRIO version 1.3

- Class 1+ End Point Device

◆ 10 Gbps Throughput

- 18Mbit Internal Density

- **Programmable Target Address**

- **Packet Tally Indicator**

- **Packet Interval Timer**

- Replace Missing Packet

- Optional External QDR SRAM Available

- Up to 72Mbit external QDR SRAM QDR SRAM, 200 MHz; (18M, 36M, 72M)

- Seamless Integration of Internal and External Memory

- Internal and external memory functions as a single buffer

- Single Port Buffering

- Status Flags for Combined Internal/External Memories

- Full, Empty, Partially Empty, Partially Full

- Direct or polled operation of flag status bus

- **Optional Watermark**

- Serial Buffer can Either Send a Flag or Transmit Data at a Specific Packet

- Interface I<sup>2</sup>C Interface Port

- One  $I^2C$  port for maintenance and error reporting

- Interface JTAG Interface

- JTAG Functionality for boundary scan and programming

- High-Speed CMOS Technology

- 1.2V Core operation with 3.3/2.5V JTAG interface

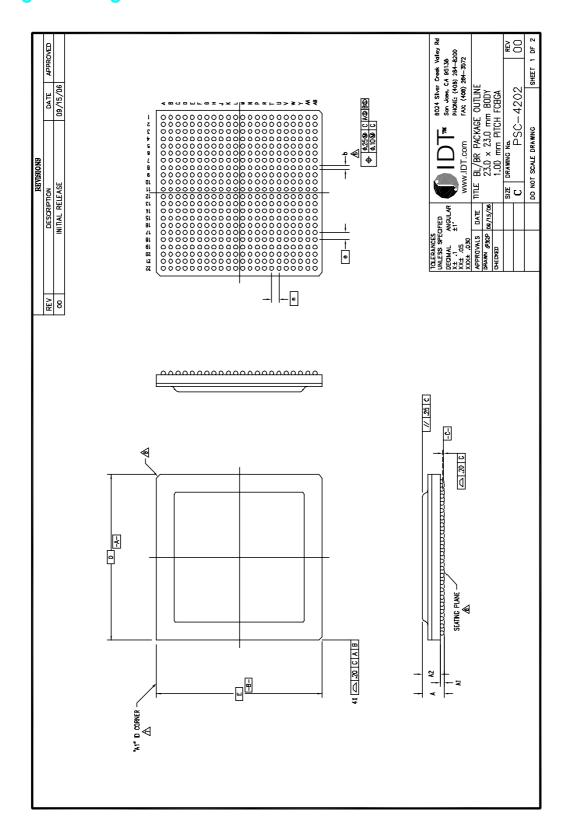

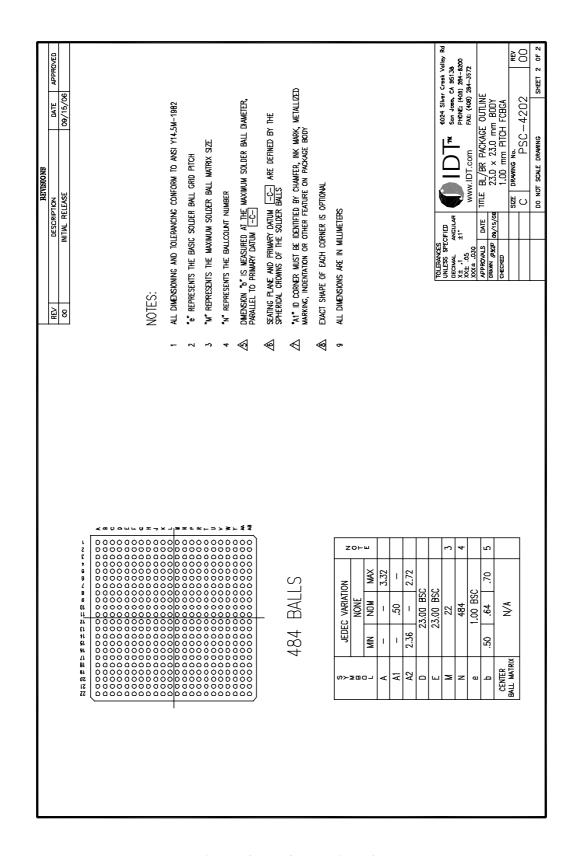

- Package: 484-pin Plastic Ball Grid Array

- 23mm x 23mm, 1.0mm ball pitch

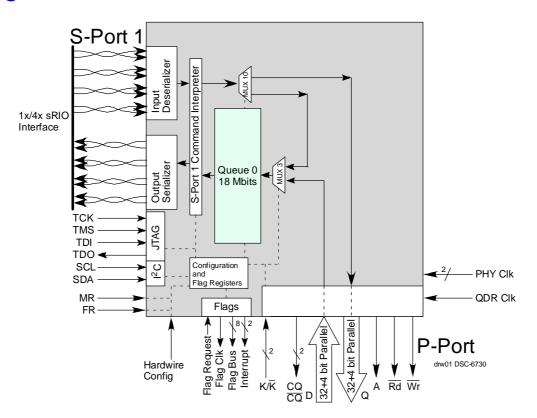

# **Block Diagram**

| IDT 80KSBR200 | Advanced Datasheet* |

|---------------|---------------------|

| Notes         |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

| IDT 80KSBR200 |  | Advanced Datasheet |

|---------------|--|--------------------|

| N | O, | ł۵ | c |

|---|----|----|---|

|   |    |    |   |

|  |   | _        |              |     |

|--|---|----------|--------------|-----|

|  | h | $\sim$ t | <br>$\sim$ r | nts |

|  | u |          |              |     |

| 1.0 Functional Description                | 9        |

|-------------------------------------------|----------|

| Interface Overview                        | 10       |

| 2.0 Applications                          | 13       |

| PPS Data Storage                          | 13       |

| Compatible External Memory                | 13       |

| 3.0 Protocols                             | 15       |

|                                           |          |

| SerB Packet Characteristics               | 15       |

| sRIO Specification                        | 15       |

| sRIO Simplified Overview The sRIO Packet  | 17<br>18 |

| The sRIO Control Symbols                  | 24       |

| Use of CRC and CRC Errors                 | 24       |

| Parallel Port Interface                   | 24       |

| 4.0 Data Handling                         | 25       |

|                                           |          |

| Inputting Data to the Queues              | 25<br>25 |

| Outputting Data from the Queues           | 25       |

| Use of Acknowledgements Idles             | 26<br>27 |

| Case Scenarios                            | 27<br>27 |

| Water Levels and Watermarks               | 28       |

| Missing Packet Detection and Replacement  | 29       |

| Packet Tally Indicator                    | 31       |

| Packet Interval Timer                     | 31       |

| Protocol Translation                      | 31       |

| 5.0 Doorbells and Interrupts              | 33       |

| Doorbell Characteristics                  | 33       |

| External Interrupt Pins                   | 34       |

| 6.0 Device Programming                    | 35       |

|                                           |          |

| Vendor IDs                                | 35       |

| Memory Map                                | 35       |

| Programming and Reset                     | 37       |

| 7.0 Error Management                      | 41       |

| sRIO Errors and Error Handling            | 41       |

| System Software Error Notification        | 41       |

| sRIO Errors Supported                     | 42       |

| Other SerB Errors                         | 61       |

| 8.0 Registers                             | 63       |

| sRIO Registers                            | 63       |

| Configuration Registers                   | 88       |

| SerB Error Counter Registers              | 100      |

| Serdes Quad Control Registers             | 102      |

| Flag and Flag Mask Registers              | 102      |

| 9.0 Reset and Initialization              | 111      |

| Speed Select                              | 111      |

| sRIO Reset Control Symbol                 | 111      |

| JTAG Reset                                | 111      |

| System Initialization                     | 111      |

| Initialization of RIO Ports               | 112      |

| 10.0 Reference Clock                      | 113      |

| Reference Clock Electrical Specifications | 113      |

| 11.0 Absolute Maximum Ratings             | 114      |

| IDT 80KSBR200 |                                                         | Advanced Datasheet |

|---------------|---------------------------------------------------------|--------------------|

| Notes         | Recommended Temperature and Operating Voltage           | 115                |

| 110100        | AC Test Conditions                                      | 115                |

|               | 12.0 I <sup>2</sup> C-Bus                               | 117                |

|               | I <sup>2</sup> C Device Address                         | 117                |

|               | Signaling                                               | 117                |

|               | Figures                                                 | 118                |

|               | I <sup>2</sup> C DC Electrical Specifications           | 119                |

|               | I <sup>2</sup> C AC Electrical Specifications           | 120                |

|               | I <sup>2</sup> C Timing Waveforms                       | 121                |

|               | 13.0 Serial RapidIO <sup>tm</sup> AC Specifications     | 123                |

|               | Overview                                                | 123                |

|               | Signal Definitions                                      | 123                |

|               | Equalization                                            | 124                |

|               | Explanatory Note on XMT and RCV Specifications          | 124                |

|               | Transmitter Specifications                              | 124                |

|               | Receiver Specifications                                 | 127                |

|               | 14.0 Parallel Port Electrical Characteristics           | 131                |

|               | AC Electrical Characteristics                           | 131                |

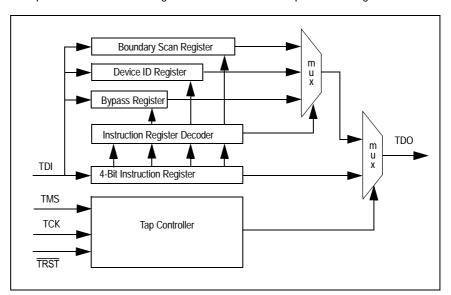

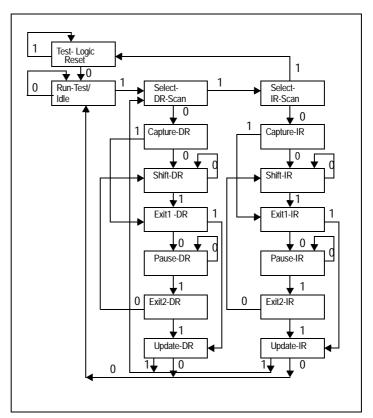

|               | 15.0 JTAG Interface                                     | 135                |

|               | IEEE 1149.1 (JTAG) & IEEE 1149.6 (AC Extest) Compliance | 135                |

|               | System Logic TAP Controller Overview                    | 135                |

|               | Signal Definitions                                      | 135                |

|               | Test Data Register (DR)                                 | 136                |

|               | Instruction Register (IR)                               | 139                |

|               | Usage Considerations                                    | 141                |

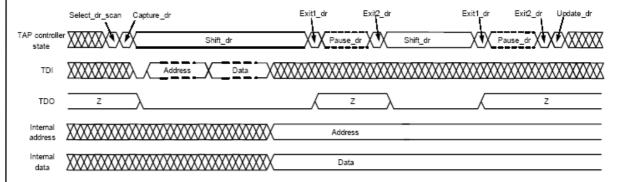

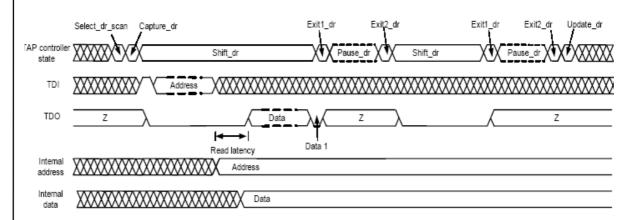

|               | JTAG Configuration Register Access                      | 142                |

|               | JTAG DC Electrical Specifications                       | 143                |

|               | JTAG AC Electrical Specifications                       | 144                |

|               | JTAG Timing Specifications                              | 144                |

|               | 16.0 Pinout & Pin Listing                               | 145                |

|               | Pinout                                                  | 145                |

|               | Pin Listing                                             | 146                |

|               | 17.0 Package Specifications                             | 169                |

|               | Package Physical & Thermal Specifications               | 169                |

|               | Package Drawings                                        | 170                |

|               | 18.0 References & Standards                             | 172                |

|               | 19.0 Revision History                                   | 172                |

|               | Advanced Datasheet: Definition                          | 172                |

|               | 20.0 Ordering Information                               | 172                |

# **Notes**

# **List of Tables**

| Table 1: SerB Memory Map                                                | 35 |

|-------------------------------------------------------------------------|----|

| Table 2: Port-write Packet Data Payload for Error Reporting             | 42 |

| Table 3: Physical RIO Errors Detected                                   | 42 |

| Table 4: Physical RIO Threshold Response                                | 44 |

| Table 5: Hardware Errors for NRead Transaction                          | 45 |

| Table 6: Hardware Errors for Maintenance Read/Write Request Transaction | 47 |

| Table 7: Hardware Errors for RIO Write Class Transactions               | 51 |

| Table 8: Hardware Errors for SWrite Class Transactions                  | 53 |

| Table 9: Hardware Errors for Maintenance Response Transactions          | 54 |

| Table 10: Hardware Errors for Response Transactions                     | 57 |

| Table 11: Hardware Errors for Reserved FType                            | 60 |

| Table 12: RIO Base Feature Address Space                                | 64 |

| Table 13: Device ID CAR                                                 | 64 |

| Table 14: Device Information CAR                                        | 65 |

| Table 15: Assembly ID CAR                                               | 65 |

| Table 16: Assembly Info CAR                                             | 65 |

| Table 17: Process Element Features CAR                                  | 66 |

| Table 18: Source Operations CAR                                         | 67 |

| Table 19: Destination Operations CAR                                    | 67 |

| Table 20: Processing Element Logical Layer Control CSR                  | 68 |

| Table 21: Local Configuration Space Base Address 1 CSR                  | 69 |

| Table 22: Base Device ID CSR                                            | 69 |

| Table 23: Host Base Device ID Lock CSR                                  | 70 |

| Table 24: Component Tag CSR                                             | 70 |

| Table 25: RIO Extended Features Address Space                           | 71 |

| Table 26: 1x/4x LP-Serial Register Block Header                         | 72 |

| Table 27: Port Link Time-out CSR                                        | 72 |

| Table 28: Port Response Time-out CSR                                    | 72 |

| Table 29: Port General Control CSR                                      | 73 |

| Table 30: Port 0 Link Maintenance Request CSR                           | 73 |

| Table 31: Port 0 Link Maintenance Response CSR                          | 74 |

| Table 32: Port 0 Local ackID Status CSR                                 | 74 |

| Table 33: Port 0 Error and Status CSR                                   | 75 |

| Table 34: Port 0 Control CSR                                            | 77 |

| Table 35: Error Management Extensions Block Header                      | 78 |

| Table 36: Logical/Transport Layer Error Detect CSR                      | 78 |

| Table 37: Logical/Transport Layer Error Enable CSR                      | 79 |

| Table 38: Logical/Transport Layer Address Capture CSR                   | 81 |

| Table 39: Logical/Transport Layer Device ID Capture CSR                 | 81 |

| Table 40: Logical/Transport Layer Control Capture CSR                   | 82 |

| Table 41: Port-write Target Device ID CSR                               | 82 |

| Table 42: Port 0 Error Detect CSR                                       | 83 |

| Table 43: Port 0 Error Rate Enable CSR                                  | 83 |

| Table 44: Port 0 Attribute Capture CSR                                  | 85 |

| Table 45: Port 0 Packet/Control Symbol Capture 0 CSR                    | 85 |

| Table 46: Port 0 Packet/Control Symbol Capture 1 CSR                    | 86 |

| Table 47: Port 0 Packet/Control Symbol Capture 2 CSR                    | 86 |

| Table 48: Port 0 Packet/Control Symbol Capture 3 CSR                    | 86 |

| Table 49: Port 0 Error Rate CSR                                         | 87 |

| Table 50: Port 0 Error Rate Threshold CSR                               | 88 |

| Table 51: Reset and Command Register                                    | 89 |

| Table 52: Serial Port Configuration Register                            | 90 |

| Table 53: Parallel Port Configuration Register                          | 90 |

| Table 54: Memory Allocation Register                                    | 90 |

| •                                                                       |    |

| IDT 80KSBR200 |                                                                                                                               | Advanced Datasheet* |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Notes         | Table 55: Lost Packet Replacement Register                                                                                    | 91                  |

| Morez         | Table 56: Source and Destination ID Register                                                                                  | 91                  |

|               | Table 57: PAE / PAF Register                                                                                                  | 92                  |

|               | Table 58: Watermark Register                                                                                                  | 92                  |

|               | Table 59: Waterlevel Register                                                                                                 | 92                  |

|               | Table 60: Space Available Register                                                                                            | 92                  |

|               | Table 61: MBIST Control Register                                                                                              | 93                  |

|               | Table 62: QBIST Control Register                                                                                              | 93                  |

|               | Table 63: JTAG Device ID Register                                                                                             | 94                  |

|               | Table 64: Case Scenario Packet Header Register                                                                                | 95                  |

|               | Table 65: Case Scenario Start Address Register                                                                                | 95                  |

|               | Table 66: Case Scenario Next Address Register                                                                                 | 96                  |

|               | Table 67: Case Scenario Stop Address Register                                                                                 | 96                  |

|               | Table 68: Case Scenario Frame Register                                                                                        | 97                  |

|               | Table 69: Missing Packet Start Address Register                                                                               | 97                  |

|               | Table 70: Missing Packet Current Address Register                                                                             | 98                  |

|               | Table 71: Missing Packet Address Increment Register                                                                           | 98                  |

|               | Table 72: Missing Packet Stop Address Register                                                                                | 98                  |

|               | Table 73: Data Packet Interval Timer Register                                                                                 | 99                  |

|               | Table 74: Doorbell Packet Interval Timer Register                                                                             | 99                  |

|               | Table 75: Missing Packet Size Register                                                                                        | 99                  |

|               | Table 76: Missing Packet Address Logging Register                                                                             | 99                  |

|               | Table 77: Missing Packet Address Logging Register for TI DSP                                                                  | 100                 |

|               | Table 78: S-Port Data Packet Received Counter                                                                                 | 100                 |

|               | Table 79: S-Port Data Packet Transmitted Counter                                                                              | 100                 |

|               | Table 80: S-Port Priority Packet Received Counter                                                                             | 101                 |

|               | Table 81: S-Port Priority Packet Transmitted Counter                                                                          | 101                 |

|               | Table 82: S-Port Packet Received Counter                                                                                      | 101                 |

|               | Table 83: S-Port Packet Transmitted Counter                                                                                   | 102                 |

|               | Table 84: SERDES Quad Control Register                                                                                        | 102                 |

|               | Table 85: Flag and Flag Mask Register                                                                                         | 103                 |

|               | Table 86: S-Port Link Status Register                                                                                         | 104                 |

|               | Table 87: Device Configuration Error Register                                                                                 | 104                 |

|               | Table 88: sRIO DMA Status Register                                                                                            | 105                 |

|               | Table 89: Missing Packet Flag Register                                                                                        | 106                 |

|               | Table 90: FIFO Queue Empty Flag Register                                                                                      | 106                 |

|               | Table 91: FIFO Queue Full Flag Register                                                                                       | 107                 |

|               | Table 92: DSP Interrupt Flag Register                                                                                         | 108                 |

|               | Table 93: Tally Doorbell Flag Register                                                                                        | 109                 |

|               | Table 94: Missing Packet Programmable Flag Register                                                                           | 109                 |

|               | Table 95: Port Speed Selection Pin Values                                                                                     | 111                 |

|               | Table 96: Input Reference Clock Jitter Specification                                                                          | 113                 |

|               | Table 97: Absolute Maximum Ratings                                                                                            | 114                 |

|               | Table 98: Recommended Temperature and Operating Voltage                                                                       | 115                 |

|               | Table 99: AC Test Conditions (Vdd3 = 3.3V / 2.5V); JTAG, I2C, RST                                                             | 115                 |

|               | Table 100: Typical Power Figures                                                                                              | 116                 |

|               | Table 101: I2C Static Address Selection Pin Configuration                                                                     | 117                 |

|               | Table 102: P-Port AC Electrical Characteristics                                                                               | 132                 |

|               | Table 103: JTAG Pin Description                                                                                               | 135                 |

|               | Table 104: Instructions Supported by 80KSBR200's JTAG Boundary Scan                                                           | 139                 |

|               | Table 105: System Controller Device ID Register                                                                               | 140                 |

|               | Table 106: System Controller Device ID Register  Table 106: System Controller Device ID Instruction Format                    | 140                 |

|               | Table 100: System Controller Device in Instruction Format  Table 107: Data Stream for JTAG Configuration Register Access Mode | 141                 |

|               | Table 107: Data Stream for STAG Configuration Register Access Mode                                                            | 142                 |

| Į.            | iasio ivo, i ili Listings                                                                                                     | טדו                 |

# Notes | List of Figures

| Figure 1: Diagram of SerB Interfaces                                                | 10  |

|-------------------------------------------------------------------------------------|-----|

| Figure 2: PPS Data Storage                                                          | 13  |

| Figure 3: Generic sRIO Request Packet                                               | 18  |

| Figure 4: sRIO Physical Layer Header                                                | 19  |

| Figure 5: Transaction Types (8 or 16)                                               | 19  |

| Figure 6: Transaction ID Range for sRIO Packet Generating Entities                  | 22  |

| Figure 7: sRIO Maintenance Request Packet (Type 8)                                  | 23  |

| Figure 8: sRIO Maintenance Response Packet (Type 8)                                 | 23  |

| Figure 9: Typical sRIO Packet showing location of Source and Destination IDs        | 27  |

| Figure 10: sRIO Doorbell Packet                                                     | 33  |

| Figure 11: Reset Timeline                                                           | 111 |

| Figure 12: REF_CLK Representative Circuit                                           | 113 |

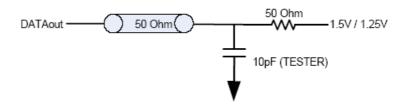

| Figure 13: AC Output Test Load (JTAG)                                               | 115 |

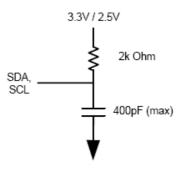

| Figure 14: AC Output Test Load (I2C)                                                | 116 |

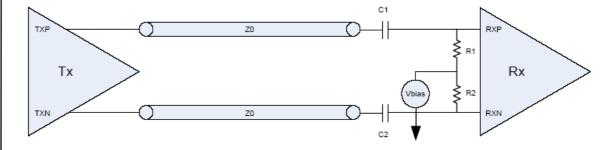

| Figure 15: sRIO Lanes Test Load                                                     | 116 |

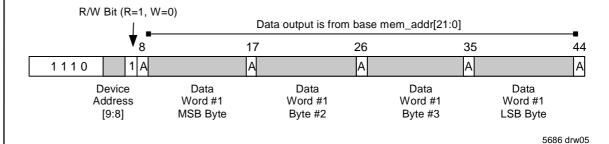

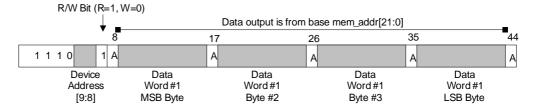

| Figure 16: Write Protocol with 10-bit Slave Address (ADS = 1)                       | 118 |

| Figure 17: Read Protocol with 10-bit Slave Address (ADS = 1)                        | 118 |

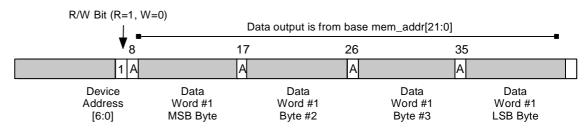

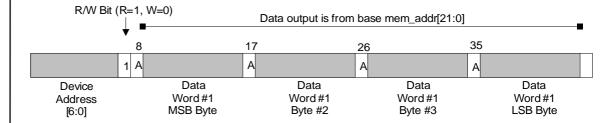

| Figure 18: Write Protocol with 7-bit Slave Address (ADS = 0)                        | 119 |

| Figure 19: Read Protocol with 7-bit Slave Address (ADS = 0)                         | 119 |

| Figure 20: I2C SDA & SCL DC Electrical Specifications (VDD3 = 3.3V)                 | 119 |

| Figure 21: I2C SDA & SCL DC Electrical Specifications (VDD3 = 2.5V)                 | 120 |

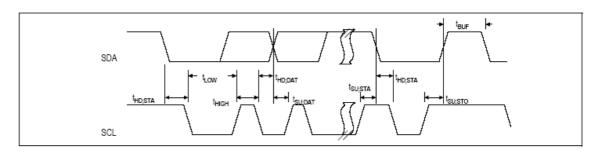

| Figure 22: Specification of the SDA & SCL bus lines for F/S-mode I2C-bus Device     | 120 |

| Figure 23: I2C Timing Waveform                                                      | 121 |

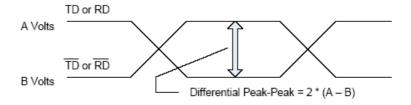

| Figure 24: Differential Peak-Peak Voltage of Transmitter or Receiver                | 123 |

| Figure 25: Short Run Transmitter AC Timing Specifications - 1.25 GBaud              | 124 |

| Figure 26: Short Run Transmitter AC Timing Specifications - 2.5 GBaud               | 125 |

| Figure 27: Short Run Transmitter AC Timing Specifications - 3.125 GBaud             | 125 |

| Figure 28: Long Run Transmitter AC Timing Specifications - 1.25 GBaud               | 125 |

| Figure 29: Long Run Transmitter AC Timing Specifications - 2.5 GBaud                | 126 |

| Figure 30: Long Run Transmitter AC Timing Specifications - 3.125 GBaud              | 126 |

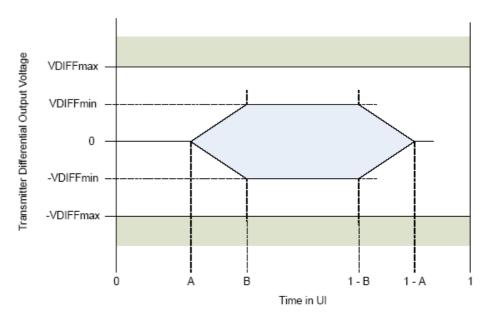

| Figure 31: Transmitter Output Compliance Mask                                       | 127 |

| Figure 32: Transmitter Differential Output Eye Diagram Parameters                   | 127 |

| Figure 33: Receiver AC Timing Specifications - 1.25 GBaud                           | 128 |

| Figure 34: Receiver AC Timing Specifications - 2.5 GBaud                            | 128 |

| Figure 35: Receiver AC Timing Specifications - 3.125 GBaud                          | 129 |

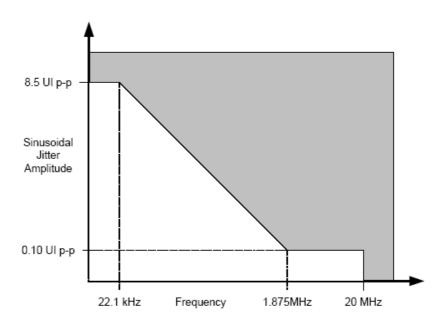

| Figure 36: Single Frequency Sinusodial Jitter Limits                                | 129 |

| Figure 37: Receiver Input Compliance Mask                                           | 130 |

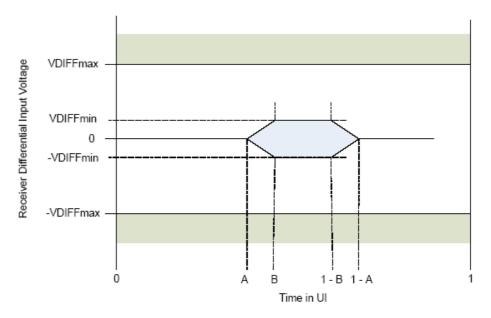

| Figure 38: Receiver Input Compliance Mask Parameters Exclusive of Sinusodial Jitter | 130 |

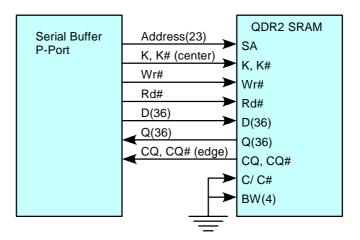

| Figure 39: P-Port Signals Connected to a QDRII SRAM                                 | 131 |

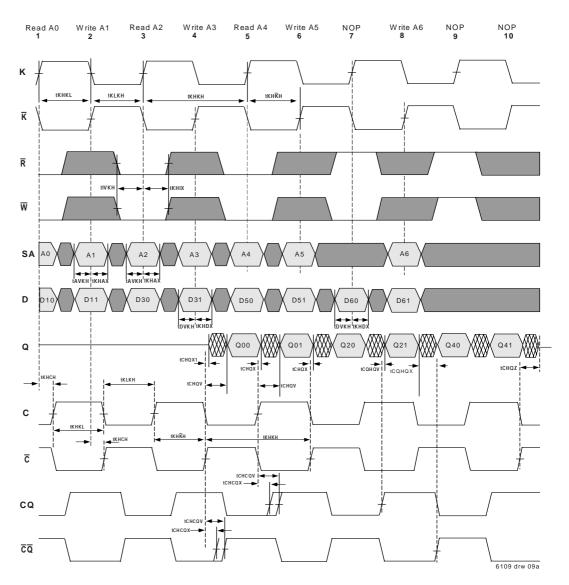

| Figure 40: Timing Waveform of Combined Read and Write Cycles                        | 133 |

| Figure 41: Diagram of the JTAG Logic                                                | 135 |

| Figure 42: State Diagram of the 80KSBR200's TAP Controller                          | 136 |

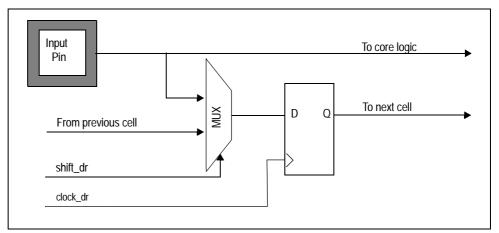

| Figure 43: Diagram of Observe-only Input Cell                                       | 137 |

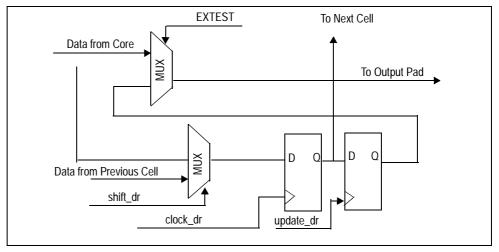

| Figure 44: Diagram of Output Cell                                                   | 137 |

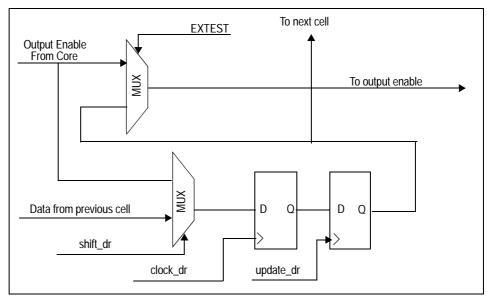

| Figure 45: Diagram of Output Enable Cell                                            | 138 |

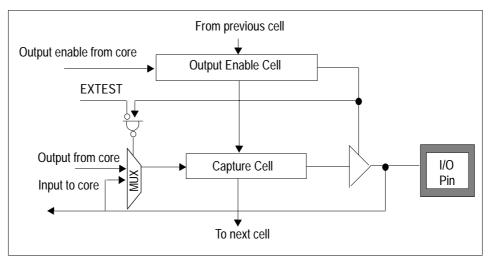

| Figure 46: Diagram of Bi-directional Cell                                           | 138 |

| Figure 47: Implementation of Write during Configuration Register Access             | 142 |

| Figure 48: Implementation of Read during Configuration Register Access              | 143 |

| Figure 49: JTAG DC Electrical Specifications (VDD3 = 3.3V)                          | 143 |

| Figure 50: JTAG DC Electrical Specifications (VDD3 = 2.5V)                          | 143 |

| Figure 51: JTAG AC Electrical Specifications                                        | 144 |

| Figure 52: JTAG Timing Specifications                                               | 144 |

|                                                                                     |     |

| IDT 80KSBR200 |                                          | Advanced Datasheet* |

|---------------|------------------------------------------|---------------------|

| Notes         | Figure 53: 80KSBR200 Pinout              | 145                 |

| MOTES         | Figure 54: SerB Package Drawing (1 of 2) | 170                 |

|               | Figure 54: SerB Package Drawing (2 of 2) | 170                 |

|               |                                          |                     |

#### **Notes**

# 1.0 Functional Description

The IDT80KSBR200 is a Serial RapidIO<sup>™</sup> sequential buffer (SerB) flow-control device consisting of up to 18Mbits of on-chip memory with expansion of one QDR SRAM externally bringing the total buffering capacity to 90Mbits of storage. This device is built to work with any sRIO device and especially with the IDT Pre-Processing Switch (PPS) number IDT70K200.

In this configuration, the main application is working in conjunction with the PPS. In applications were multiple DPSs are used with the PPS, the SerB can function as an over-flow port to handle traffic that is block on any given port or, as a delay buffer to store data and present it at a later time. This is important in DPS applications were time samples are compared with the previous sample such as Cellular Base Stations. Please refer to the application note "Serial Buffer and Pre-Processing Switch".

The SerB fully complies to the sRIO specification version 1.3 and is implemented to a class 1+ end-point device.

This device operates as a master. In the sRIO environment, a master is defined as a device that originates data transfers, either to or from that device. A slave is one that responds to commands from other devices to move data. As a master, the SerB can receive data and at a pre-programmed water level (number of packets), the device will form and transmit either packets or status (e.g., doorbells) to a programmed location.

The SerB performs buffering and off-loading of data as well as buffer-delay of data samples in various environments. This device can act as a master in which the SerB writes data to a programmed location once the criteria have been meet. This combination of storage and flexibility make it the perfect buffering solution for sRIO systems.

For applications requiring larger buffers, an additional 72Mbits of QDR SRAM can be attached via the Parallel Port. The two memories are seamlessly connected by the Serial Buffer to form a large, 90 Mbit buffer memory. The QDR SRAM interface runs at speeds of only 156.25MHz allowing lower cost memories to be used as well as easier board layout. Data rates still support up to 10Gbits/s (OC-192) thoughput in the device to maintain full sRIO four-lane compliance.

The device provides Full flag and Empty flag status for the queue for write and read operations respectively. Also a Programmable Almost Full and Almost Empty flag for the queue is provided.

A JTAG test port is provided running at 3.3V, device has a fully functional Boundary Scan feature, compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture. The SerB can also be programmed via the JTAG port. There is also an I<sup>2</sup>C processor port for programming and retrieving information from the configuration registers.

The device is configured into a single queue comprising the full internal memory and potentially the external memory if attached. The device treats the full amount of memory, wether internal or a combination of internal and external, as a single memory block. Status flags from that queue, either referring to the writes (full flags) or the reads (empty flags) to or from that queue represent the total amount of memory. Flags can be read from the serial port or from the I<sup>2</sup>C or JTAG port. Proactive flags can be configured to send a doorbell and/or change the interrupt pin once a flag is set. Partial full and empty flags can be programmed to provide reaction time for writes and reads respectively. Flags associated with reaching water marks are available in addition to the full and empty flags.

Further information regarding this device and follow-on devices with added functionality are available from IDT.

### **Notes**

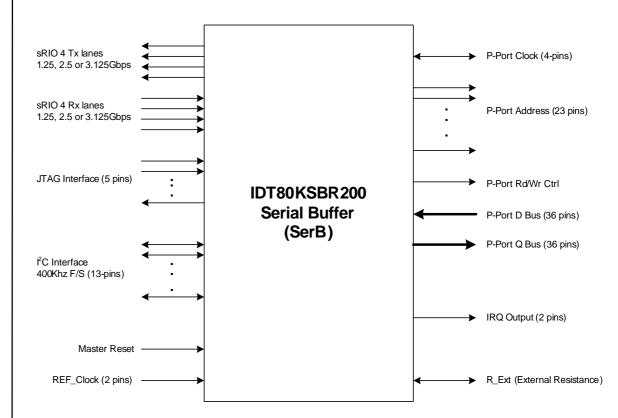

### 1.1 Interface Overview

Figure 1 Diagram of SerB Interfaces

### 1.1.1 sRIO Port

The sRIO interface is the main communication port on the chip. This port is compliant with the serial RapidIO<sup>TM</sup> v. 1.3 specifications. Please refer to the serial RapidIO<sup>TM</sup> specifications for full detail.

There are 4 uni-directional differential links for a total of 8 pins. Each can run at 1.25, 2.5, or 3.125Gbps programmable. Both sRIO data (sample) and maintenance packets are transmitted and received on these links.

### 1.1.2 Parallel Port

P-Port interface is used as a memory expansion port. As a memory expansion port, one of the designated QDR SRAM devices can be connected. If P-Port is connected to one of the designated SRAM devices, it will maintain the clocking and full interconnection to drive the SRAM device.

### 1.1.3 I<sup>2</sup>C Bus

This interface may be used as an alternative to the standard sRIO or JTAG ports to program the chip and to check the status of registers - including the error reporting registers. It is fully compliant with the  $I^2C$  specification, It has 13 pins and supports both Fast- and Slow-mode buses [1]. Refer to the " $I^2C$ " chapter for full detail.

#### 1.1.4 JTAG TAP Port

This TAP interface is IEEE1149.1 (JTAG) and 1149.6 (AC Extest) compliant [10, 11]. It may also be used as an alternative to the standard sRIO or  $I^2C$  ports to program the chip and to check the status of registers - including the error reporting registers. It has 5 pins. Refer to the JTAG chapter for full detail.

### **Notes**

# 1.1.5 Interrupt (IRQ)

An interrupt output is provided in support of Error Management functionality. This output may be used to flag a host processor in the event of error conditions within the device. Refer to the Error Management section for full detail.

#### **1.1.6 Reset**

A single Reset pin is used for full reset of the SerB, including setting all registers to power-up defaults. Refer to the Reset & Initialization section for full detail.

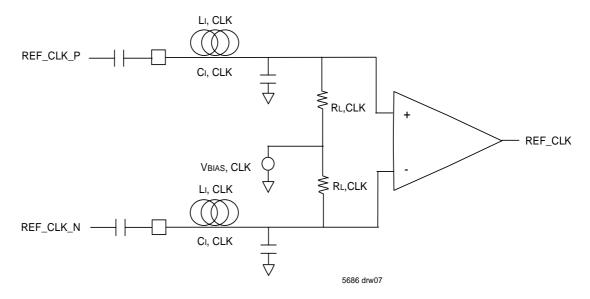

### 1.1.7 Clock

The single system clock (REF\_CLK+ / -) is a 156.25 MHz differential clock input. Refer to the Clock section for full detail.

# 1.1.8 R-Ext (Rextn & Rextp)

These pins are used to establish the drive bias on the SERDES output. An external bias resistor is required. The two pins must be connected to one another with a 12k Ohm resistor. This provides CML driver stability across process and temperature.

### 1.1.9 SPD[1:0]

Speed Select Pins. These pins define the sRIO port speed at RESET. The RESET setting may be overridden by subsequent programming of the Serial Port Configuration Register. SPD[1:0] = {00 = 1.25G, 01 = 2.5G, 10 = 3.125G, 11 = RESERVED}. These pins must remain STATICALLY BIASED after power-up.

| IDT 80KSBR200 | Advanced Datasheet* |

|---------------|---------------------|

| Notes         |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

|               |                     |

12 of 172 March 19, 2007

"2005 Integrated Device Technology, Inc. All rights reserved. Advanced Datasheet for informational purposes only. Product specifications subject to change without notice. NOT AN OFFER FOR SALE The information presented herein is subject to a Non-Disclosure Agreement (NDA) and is for planning purposes only. Nothing contained in this presentation, whether verbal or written, is intended as, or shall have the effect of, a sale or an offer for sale that creates a contractual power of acceptance.

### **Notes**

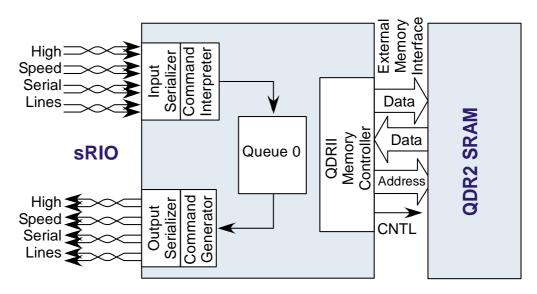

# 2.0 Application

## 2.1 PPS Data Storage

The SerB's primary application is for a Basestations using the IDT's Pre-Processing Switch (PPS). The SerB will be a storage device, holding large amounts of data passed to it by the PPS and with all of its internal memory allocated to queue 0. In this application, the S-Port on the SerB will connect to one of the 4x ports of the PPS. The PPS will pass approximately 10ms of data to the SerB at which time the SerB will start to pass it back to the PPS as a multicast. It is expected that the data flow will remain constant with 10ms (or other designated quantity) worth of data always in storage. The Basestation uses the data for decryption purposes.

The following are items of note concerning the PPS application:

- The SerB has the ability to act as a simple master.

- The SerB's application with the PPS will be to broadcast data. It must be a master to perform a broadcast, even if the data is requested.

- The SerB has the ability to initiate writes. Mainly to prevent overflow and to perform broadcasts when waterlevel is reached (timed event). This avoids requiring the DSP to increase congestion by requesting data and controlling the SerB.

- The SerB will typically perform SWRITEs.

- The target address(s) generated by the SerB is programmable.

- The packets are stored in the format they come in and are rebroadcast with simple changes to the headers

- The DSPs have the ability to read the SerB registers through the PPS.

- The DSP may send a maintenance read/write packets to the SerB requesting register information.

Figure 2 PPS Data Storage

# 2.2 Compatible External Memories

The P-Port, as a FIFO controller shall connect to an external memory device. There are two designated memory devices, which may be connected to the SerB. These are:

- QDRII-B4 SRAM with 36-bit bus in 36M size

- ◆ QDRII-B4 SRAM with 36-bit bus in 72M size

Only one memory may be connected to the P-Port at a time. **Initial release of the SerB will only support 72M density and support of other devices listed above to follow with subsequent release**. Expansion is available only through increased memory size.

### 2.2.1 Memory Default Configurations:

The memory default configuration on power up or hard reset is as follows:

### **Notes**

- No external memory is allocated, regardless of whether external memory is present.

- All SRAM is allocated to queue 0

- P-Port outputs default to valid states to prevent possible damage to external devices, unless P-Port is physically disabled by the external pin.

#### **Notes**

### 3.0 Protocol

The SerB is a packet-handling device. The SerB may be configured to require all packets to be acknowledged, and hold all packets available for retransmission until acknowledgement is received. Incoming corrupted packets are dropped and issues a retransmission request. The negotiation for acknowledgement, retransmission and dropping packets is handled at the local interface level, without intervention of higher-level authorities. The SerB does not forward any packet until it is fully received, verified, and acknowledged (if configured to verify).

### 3.1 SerB Packet Characteristics

### 3.1.1 Maximum Packet Size

The sRIO specification requires a maximum packet size of 256 bytes plus overhead. The SerB fully complies to this specification.

#### 3.1.2 Interface Packet Buffer Size

The sRIO specification has defined buffer sizes for the transmit and receive buffers. Included in the buffer specification is the requirement to transmit higher priority packets first. Upon transmission failure, and retransmission, the retransmission may be held up and a higher priority packet interjected if one arrives.

#### 3.1.3 Multicast Packets

The SerB has no special multicast capabilities. To perform a multicast, the case scenario should be set up to perform an SWRITE function. The destination ID for the case scenario should be set to a multicast address elsewhere in the system. The SerB shall perform a multicast by sending the SWRITE to the user designated multicast address, along with the data.

Waterlevel multicast in the PPS application is done the same way. When the waterlevel event is triggered, the SerB issues an SWRITE multicast packet to the PPS multicast address. The SWRITE command is generated by the case scenario.

# 3.2 sRIO Specification

The SerB serial interface is a standard 1x/4x serial port with sRIO capabilities. In the PPS application, the sRIO port act primarily as an sRIO end-point, but will work as a bus master to perform multicast operations.

All the RIO TWG documents can be found on the RapidIO Members website:

http://www.rapidio.org/apps/org/workgroup/twg/documents.php

The following documents are the final version 1.2 specifications, which can be found under the Members Library section, version 1.3 of the specifications will replace these section files when they are approved by the Steering Committee:

**RapidIO\_Spec.pdf** Part I through part IV of the spec., version 1.2

gsmlspec.pdfPart V of the spec., version 1.2serial.book.pdfPart VI of the spec., version 1.2inter-op.pdfPart VII of the spec., version 1.2errspec.pdfPart VIII of the spec., version 1.2errata1.pdfErrata 1 to version 1.2 of the spec.fcspec.pdfPart IX of the spec., version 1.0

**system\_bringup\_spec.pdf** Annex I of the spec.

The version 1.3 files are currently:

IO\_logical.pdfPart 1: Input/Output Logical Specificationmsg\_logical.pdfPart 2: Message Passing Logical Specificationcmn\_trnspt.pdfPart 3: Common Transport Specification

parallel\_phy.pdf Part 4: Physical Layer 8/16 LP-LVDS Specification

#### Notes

qsmlspec.pdf Part 5: Globally Shared Memory Specification serial book.pdf Part 6: 1x/4x LP-Serial Physical Layer Specification inter-op.pdf Part 7: System and Device Inter-operability Spec errspec.pdf Part 8: Error Management Extensions Specification fcspec.pdf Part 9: Flow Control Logical layer Specification encapspec.pdf Part 10: Data Streaming logical Specification mcspec.pdf Part 11: Multicast Extensions Specification sbtg.pdf Annex 1: Software/System Bring Up Specification

There is a checklist for compliance to version 1.3 of the RIO specification, which will be used to insure proper RIO operation.

### 3.2.1 RapidIO Spec. Version 1.3

In compliance with the sRIO specification, the port has the ability to connect directly to a 1x/4x sRIO port on the PPS device, or connect to any other sRIO compliant 1x/4x port. This includes the standard lane fail functions where a failure of any lane on a 4x port will force the device into a 1x operation on lane 0 or lane 2. The SerB has no requirement to perform with more than a single 1x port. Restated, S-Port shall be either a 4x port or a 1x port as designated by the configuration or fail mode, but shall never be four 1x ports operating simultaneously.

The RIO specification is a universal specification and all sections do not fully apply to the SerB. Each of the parts of the specification will be listed individually below along with the compliance level for the SerB. Some of the documents are not complete and published. Some are working group showings.

Each chapter is discussed in a separate section below.

Part 1: Input/Output Logical Specification

The SerB device shall abide by this spec.

Part 2: Message Passing Logical Specification

The SerB device shall abide by this spec.

Part 3: Common Transport Specification

The SerB device shall abide by this spec.

Part 4: Physical Layer 8/16 LP-LVDS Specification

The SerB device does not support this spec.

Part 5: Globally Shared Memory Logical Specification

The SerB device does not support this spec.

Part 6: Physical Layer 1x/4x LP-Serial Specification

The SerB shall abide by this spec.

Part 7: System and Device Inter-operability Specification

The SerB device shall comply with the Generic Class Requirements (class 1+).

Part 8: Error Management Extensions Specification

The SerB device shall comply with this spec.

Part 9: Flow Control Logical Layer Specification

The SerB devices does not support this spec.

Part 10: Data Streaming Logical Specification

The PPS device does not support this spec.

Part 11: Multicast Extensions Specification

SerB device shall abide by this spec (do nothing). A multicast for SerB is a simple write to an address.

#### **Notes**

### Annex I: Software/System Bring Up Specification

Already comply.

#### Approved Showings

The following documents are approved showings in the TWG. Each of them will be discussed in detail.

### 04-11-00031.001

Change to the spec of the Serial RapidIO Receiver Sinusoidal Jitter Tolerance Mask. IDT SerDes is tuned to this spec.

### 3.2.2 Summation of RIO registers

The SerB shall include all registers required by the RIO spec for configuration.

#### 3.2.3 sRIO Priorities

sRIO has two forms of priority. The first is the Standard sRIO priority. The second is the Virtual Channel form of sRIO. There is a bit set in the data stream where VC = 0 designates standard sRIO priorities, while VC = 1 designates virtual channels. The SerB shall not use virtual channels, but pass any virtual channel data as if it were sent with standard priority.

Standard sRIO has four discrete levels of priority (two bits). Added to the priority is the CRF (Critical Request Flow) bit which is a priority distinguishing bit within a priority (LSB), bringing the total number of priority bits to three. High priority packets are always sent before lower priority packets. Low priority packets do not enter the data stream until the high priority packets are exhausted. The SerB ignores the CRF bit.

In virtual channel prioritization, there are three bits that designate the virtual channel. These replace the sRIO two bit priority plus CRF bit. With virtual channels, each channel is allocated a percentage of the total bandwidth. In this application, all channels are allocated some bandwidth regardless of their priority, preventing high priority packets from stealing the entire bandwidth. The SerB shall not support Virtual Channels, but instead will always transmit higher priority packets first.

The sRIO user may transmit data on any priority with little regard to volume of data. For instance if there operating at close to full bandwidth with critical data, but would like to support additional service on an "as bandwidth available" basis, he may be running with most traffic on the higher priorities and limited capacity on low priorities.

The response packet sent in most applications is intended to be sent at one priority level higher than the received packet, which would limit the usage of the top priority to response packets, but it is not guaranteed that the user would not use the highest priority for other data.

# 3.3 sRIO Simplified Overview

The operation of the sRIO bus is contained in the sRIO specification. The following comments are provided to provide a superficial understanding of the initialization of the interface, without researching the specifications.

### 3.3.1 sRIO Sync

The sRIO sync is accomplished by the transmitter sending continuous /K28.5/ codes (commas) on each lane until sync is accomplished. The state machine is shown on page VI-58 of the Physical Layer x1/x4 LP-Serial Specification for RapidIO. The sync is tolerant of occasional /INVALID/ code groups as shown in the state machine and will increase or decrease level of sync, based upon the error level of the interface. Upon completion of sync, each serial lane should be able to successfully transmit and receive 8B/10B codes.

#### 3.3.2 sRIO Alignment

After sync, the lane alignment must be completed. This is accomplished by sending continuous /A/s on all lanes. The / A/s are counted until lane alignment is accomplished. The state machine for the "A" counters is shown on page VI-60 of the LP-Serial Specification for RapidIO. The state machine is tolerant of an occasional /INVALID/ code group, and will increase or decrease the state of alignment (NOT\_ALIGNED to ALIGNED\_3) based upon the successful transfer of /A/s on the lanes. A fully successful alignment would enable the 4x mode of sRIO. If links are broken and/or alignment is not possible, the interface will be required to operate with a single link (lane 0 or 2).

#### **Notes**

#### 3.3.3 sRIO Mode Initialization

Once sync and alignment is accomplished, the sRIO controlling device will search for the SerB. The steps of the search include SILENT, SEEK, and then DISCOVERY. Once DISCOVERY is complete, the mode will be set to 4X\_MODE (optimum performance), 1X\_MODE\_LANEO, or 1X\_MODE\_LANE2, depending upon the success of establishing the link. The state machine for the MODE is shown on page VI-64 of the LP-Serial Specification for RapidIO.

#### 3.3.4 sRIO Control Symbols

sRIO requires the transmission of control symbols providing link status every 819.2ns or less whenever the link is otherwise idle. The control symbols are described in section 5.2 of the LP-Serial Specification for RapidIO. These include delimiters /K28.3/ if a packet delimiter is included or /K28.0/ if there is no packet delimiter.

### 3.3.5 sRIO End-to-End Retransmissions

As an sRIO bus endpoint, the SerB supports end-to-end sRIO retransmissions. This is required for the SerB to meet the sRIO compliance testing as an endpoint. When S-Port is acting as an sRIO slave, the SerB fully acknowledges all link-to-link transactions and end-to-end transactions per the sRIO specification.

As an sRIO bus master, as would be the case with a waterlevel or doorbell master, the SerB has limited capabilities. At the link level, the SerB has the ability to receive acknowledgement of all transactions at the link level and perform retransmissions of any packets for which a retransmission has been requested.

The SerB does not have the ability to support end-to-end retransmissions as a bus master. When a packet is sent out from the SerB as a bus master, an end-to-end response packet should be received in due time. The packet will be handled as follows:

- If the response is an acknowledgement -- the response will be ignored.

- If the response is a retransmission request a flag will be set and the packet otherwise ignored. No retransmission will be attempted.

- If there is no response the SerB will not realize there was no response, because it was not looking for one.

### 3.3.6 The SerB as an sRIO System Host

The SerB has no ability to act as a host in an sRIO system. The SerB does have the ability to act as a bus master on occasion and will take control of the bus to accomplish the transmission of selected data items or perform selected functions. The SerB does not have the ability to control a system or fully interact and interpret the actions of other devices in the system. Bus mastering is limited to the transmission of the designated data.

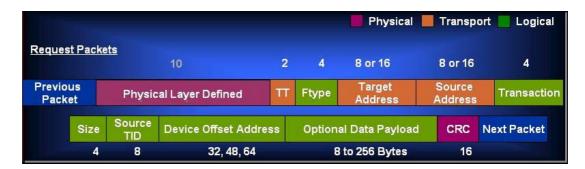

### 3.4 The sRIO Packet

sRIO has a defined packet structure for each type of packet. The sRIO specification should be referenced for a complete description of sRIO packets and their architecture. Packet aspects that are significant in the SerB are described here for clarity, but the sRIO specification overrides in the event of a discrepancy.

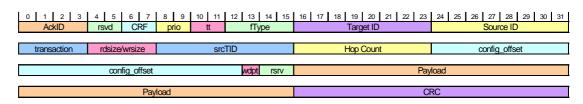

Figure 3 Generic sRIO Request Packet

Looking at Figure 3, the sRIO packet contains the following items:

- Physical Layer Defined header, shown in Figure 4.

- The transaction type, TT, that defines 8 or 16 bit device ID fields, shown in Figure 5.

172 March 19, 2007

#### **Notes**

- The Ftype, which defines the type of packet being sent. The types are shown in section 3.4.4.

- The Target Address, a.k.a Destination ID. This will be 8 bits or 16 bits, depending upon the state of TT.

- The Source Address, a.k.a Source ID. This will be 8 bits or 16 bits, depending upon the state of TT.

- The Transaction, which is dependent upon the packet Ftype. The supported transactions are described individually.

### 3.4.1 sRIO Physical Layer Header

The sRIO physical layer header is shown in Figure 14. The various fields are defined in the sRIO Physical Layer 1x/4x specification. The sRIO priority is the priority of the packet during transmission. The contents of the physical layer do not go beyond the interface, except the packet priority (Pri) may be dictated for any transmitted packet. In the SerB, there are two methods for setting the priority.

- If a transmitted packet is a response to a received packet, the sRIO response priority will be one priority level higher than the priority of the request packet, up to the maximum priority.

- If the transmitted packet is being initiated by the SerB, the priority of the packet will be dictated by the SerB. In most cases, the priority will be dictated by the "Case Scenario".

Figure 4 sRIO Physical Layer Header

#### 3.4.2 sRIO Physical Layer CRC

CRC-16 accompanies all sRIO packets and is defined in the sRIO Physical Layer 1x/4x specification. The location of CRC within the packet is shown in Figure 3.

# 3.4.3 sRIO Transport Layer Header (8/16 bit Device IDs)

During sRIO "bring up", the SerB shall support both 8 and 16 bit device ID fields. Once configured as either 8 or 16 bit, the SerB does not support the other type and will drop packets once configured.

Considering that the only packet type supported is the type configured, the TT bits within the packet are not useful. The SerB insures that the proper TT bits are included in every packet sent. Incoming packet TT bits are a "don't care".

Within the sRIO packet, the TT (transaction type) is used to identify the size of the fields as shown in Figure 5.

| TT | Definition              |

|----|-------------------------|

| 00 | 8-Bit Device ID Fields  |

| 01 | 16-Bit Device ID Fields |

| 10 | Reserved                |

| 11 | Reserved                |

Figure 5 Transaction Types (8 or 16)

The source and destination IDs in the sRIO packet will be either 8 or 16 bit as configured. Every sRIO packet that the SerB generates contains a Target ID that has been generated from one of following ways:

- The packet is in response to a request. The Target ID is the source ID of the requestor.

- The packet is generated by the SerB through a "case scenario". The Target ID is included in the case scenario.

- Any packet that is generated by a case scenario will use the Source ID of the queue to send the packet.

- Any flag associated with a gueue will use the Source ID of the gueue to send the doorbell.

### **Notes**

Any packet that is generated by the SerB that is unrelated to a particular queue (such as a link error) will use

the device ID of the SerB as the source ID.

### 3.4.4 sRIO Request Packet Types (Ftype 0 - 11)

Within the sRIO specification, 16 packet types may be formed. Packet types "Type 0" through "Type 11" are Request packet types. Packet types, "Type 12" through "Type 15" are Response packet types. Many of the packet types are reserved.

The SerB has limited sRIO functionality, but should be able to imitate any type of command. The SerB initiates commands through the Case Scenario. Case Scenarios have the ability to initiate any type of command by simply entering the correct Ftype and the rest of the sRIO header as desired. The required data may be appended as needed.

The SerB fully supports only selected sRIO commands. The user needs to be aware of the limited SerB functionality, but may be able to pass commands outside the SerB limits if the usage and expectation of the commands fits within the limits of SerB capabilities.

Following are the sRIO commands SerB is capable of supporting:

- ◆ SWRITE (type 6)

- CAR/CSR (type 8)

- DOORBELLS (type 10)

- MESSAGES (type 11) (no defined message)

Following are the sRIO commands supported in next phase of SerB:

- ◆ NREAD (type 2)

- NWRITE (type 5)

- NWRITE\_R (type 5)

The packet types are described in the <u>RapidIO Interconnect Specification</u>, <u>Part 1: Input/Output Logical Specification</u> in chapter 4. The following is a list of the packet types and the level of support the lite protocols shall offer.

#### Type 0 Packet Format (Implementation Defined)

Type 0 packets shall not be used on the SerB.

## Type 1 Packet Format (Reserved)

Type 1 packets are not defined in the sRIO spec and shall not be used in the SerB. If received, they are simply passed unaltered at the logical level.

#### Type 2 Packet Format (Request Class)

Type 2 packets are described in section 4.1.5 of the sRIO spec. Type 2 is used for NREAD and ATOMIC in standard sRIO. The SerB does not support neither NREAD nor ATOMIC packet format.

### Type 3-4 Packet Format (Reserved)

Type 3 and Type 4 packets are not defined in the sRIO spec and shall not be used in the SerB. If received, on the sRIO port with an SerB destination ID, an error message shall be sent. When a case scenario is loaded with type 3 or 4, the type shall be passed along with any data. No further interpretation should be needed.

#### Type 5 Packet Format (Write Class)

Type 5 packets are described in section 4.1.7 of the sRIO spec. Type 5 is used for NWRITE, NWRITE\_R, and ATOMIC in standard sRIO. As with Type 2 packets, the priority must be identified so it can be passed.

### Type 6 Packet Format (Streaming-Write Class)

Type 6 packets are described in section 4.1.8 of the sRIO spec. Type 6 has only one function (SWRITE), which is limited in scope with no response needed. Therefore, the entire SWRITE packet must be passed unaltered, except for the addition of a priority designation.

The PPSc generates SWRITE packets, so the primary packet the SerB will see in PPS applications is SWRITE. The SerB must accept SWRITE packets as they are received, because the PPS has no backpressure mechanism and a delay in packet acceptance will mean packet loss.

### **Notes**

### Type 7 Packet Format (Reserved)

Type 7 packets are not defined in the sRIO spec and shall not be used in the SerB. If received, on the sRIO port with an SerB destination ID, an error message shall be sent. When a case scenario is loaded with type 7, the type shall be passed along with any data. No further interpretation should be needed.

### Type 8 Packet Format (Maintenance Class)

Type 8 packets are described in section 4.1.10 of the sRIO Input/Output Logical Specification. These packets are the CARs and CSRs necessary for programming and reading the status/capability of the SerB. The SerB must fully support type 8 packets.

#### Type 9 Packet Format (Reserved)

Type 9 packets are not defined in the sRIO spec and shall not be used in the SerB. If received, on the sRIO port with an SerB destination ID, an error message shall be sent. When a case scenario is loaded with type 9, the type shall be passed along with any data. No further interpretation should be needed.

### Type 10 Packet Format (Doorbells)

Doorbells are not defined in the sRIO, Part 1, "Input/Output Logical Specification", but are listed as "reserved" in section 4.1.11 of that spec. The Type 10 packets are defined in the Part 2, "Message Passing Logical Specification". The SerB shall issue doorbells as defined in section below.

### Type 11 Packet Format (Messages)

There is no use identified for type 11 packets. These packets normally carry non-doorbell messages. These packets are also considered "reserved" in the "Input/Output Logical Specification", but are defined in the "Message Passing Logical Specification".

### 3.4.5 sRIO Response Packet Types (Ftype 12 - 15)

Within the sRIO specification, packet types, "Type 12" through "Type 15" are Response packet types. Of the response type packets, all are reserved except packet type 13, which will be used for all response packets. If a response packet is received with a type other than Ftype 13, the packet shall be ignored and an error flagged.

### Type 13 Packet Format (Response)

Ftype 13 packets are defined in the sRIO Part 1, "Input/Output Logical Specification" in section 4.2.3. The SerB fully supports Ftype 13 packets.

### 3.4.6 sRIO Transaction IDs

Every sRIO transaction must have an ID that cannot repeat itself within a designated time. That designated time is the time that a packet may remain alive, including all blockages, retransmissions and acknowledgements. In the case of the SerB, retransmission capabilities beyond the link level are not supported, and therefore the transaction ID is not used.

Regardless, the SerB must handle incoming transaction IDs and generate outgoing transaction IDs. The SerB will attempt to categorize outgoing transaction IDs. Within the SerB there are multiple sources of packets, where a queue may be generating packets, plus the device itself may generate packets. In some cases, one part of the device may not know what other parts are doing.

Source ID, Destination ID, and Transaction ID all are used to identify a unique packet. In addition, response packets are identified as a "response". Using all of these identifying markers guarantees that the SerB is not capable of generating a transaction ID that would interfere with those generated by another entity.

The following items describe the use of transaction IDs within the SerB.

- Incoming transaction IDs will be returned with any response packets. This includes any response messages, responses to NWRITE\_R and other packets that require responses.

- Every transaction generating portion of the SerB will have it's own unique block of transaction IDs to loop on.

- The transaction ID includes the source ID of the transaction, so we will not be interfering with other devices in the system generating transaction IDs.

- There will be 32 transaction IDs allocated to every sRIO packet generating entity within the SerB. The doorbells will be allowed more, since there may be more active at a time.

#### **Notes**

The transaction IDs are allocated per Figure 6.

| ID Range | sRIO Packet Generating Entity |

|----------|-------------------------------|

| 31-0     | Queue 0 Output                |

| 127-32   | Reserved for future use       |

| 159-128  | Device ID of the SerB         |

| 255-160  | Doorbells and reserved        |

Figure 6 Transaction ID Range for sRIO Packet Generating Entities

Source ID, Destination ID, and Transaction ID all are used to identify a unique packet. If this includes the transaction type or some additional ID, the problems of multiple identical transaction types would be solved. Response packets are identified as response packets, which identify the originator of the request, the source ID of the responder and the transaction ID. Combining these identifies a unique packet despite the possibility of otherwise conflicting transaction IDs.

### 3.4.7 sRIO Packet Blockage and Priorities

The SerB is not a switch and should not be involved in blocking packets. Despite this, the SerB may be unable to transmit packets or packets may be blocked by downstream devices, requiring the SerB to hold and retransmit packets. When connected to the PPS, the SerB should not be reordering packets based upon priority, because packets are issued based upon time in the buffer and not priority.

When the SerB is used in non-PPS applications, it may be necessary to transmit packets based upon priority. Blocked packets would be held and transmitted after subsequently received higher priority packets have been transmitted. In this situation, blockage may develop if the inflow to the SerB exceeds or equals the outflow. Typically higher priority packets would be initiated for command and symbol passing.

### 3.4.8 The sRIO Write Packet, Type 5, Special Considerations

The SerB may receive and issue both type 5, NWRITE and NWRITE\_R packets. The SerB has no ability to issue or receive any of the three ATOMIC packets. The wrsize accompanying the data will be stored as part of the packet header in the SerB to allow correct identification of the packet length for subsequent transmission of the packet as the packet leaves the SerB.

sRIO Type 5 packets assume the recipient device is addressable as a side address memory. The SerB is a FIFO and will store the data sequentially and transmit data sequentially, regardless of the address accompanying the data. The address will be stored as part of the packet header in the SerB, and may be used when the packet is again transmitted.

Despite not using the addresses for data storage, the addresses are used in some applications to detect missing packets.

#### 3.4.9 The sRIO Maintenance Packet, Type 8, Special Considerations

The sRIO Maintenance Packet is a Type 8 packet and is used for programming and/or reading the CARs and CSRs. In addition, the Port-write maintenance packet may be generated as an error response as defined by the sRIO Error Management Specification.

The sRIO Maintenance Packet allows in-band control of the SerB configuration. The RIO specifications define a number of registers for end-point devices, which is described in the Register section.

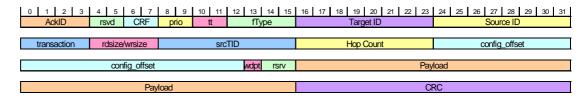

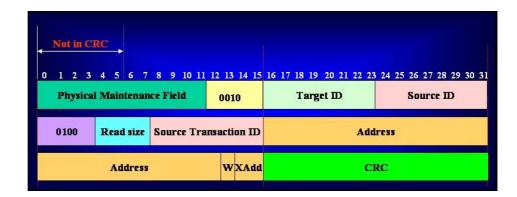

sRIO maintenance packets are Type 8 packets and have the ftype field set to 1000b. These packets are described in section 4.1.10 of the sRIO input/Output Logical spec. In addition, information on the tt and hop count can be found in section 1.3 of the Common Transport Specification. An example of the structure of a type 8 packet is shown in Figure 7. The configuration registers are all 32 bits or less, and all packets will carry 32 bits regardless of whether all 32 bits are needed.

#### **Notes**

Figure 7 sRIO Maintenance Request Packet (Type 8)

- AckID = Transaction ID for link acknowledgements

- CRF = Critical Request Flow, not used in SerB

- prio = Packet priority

- tt = Transaction type, 00 = 8 bits, 01 = 16 bits

- fType = 1000, for a type 8 maintenance packet

- Target ID = the destination ID of the SerB, is 16 bits if tt = 01

- Source ID = the ID of the sending device, is 16 bits if tt = 01

- transaction = specifies whether request is read, write and/or response, see sect 4.1.10 of sRIO Input/Output Logical spec

- rdsize/wrsize = see sect 4.1.2 of sRIO Input/Output Logical spec

- srcTID = the Transaction ID for sRIO end to end retransmissions

- Hop Count = Not important to an end point.

- config\_offset = the configuration register address

- wdptr = part of rdsize/wrsize

- Payload = 32 bits of data destined to be written to the designated register

- CRC = 16 bits of CRC

The sRIO maintenance request packet will receive a response packet as shown in Figure 8. The response will be returned to the sender of the request and include a "status" of the request. The status is identified in section 4.1.10 of the sRIO input/Output Logical spec. The SerB shall observe that 0000b indicates "done" and 0111b indicates "error".

Figure 8 sRIO Maintenance Response Packet (Type 8)

Other than the status field of the packet, the fields serve the same function as the request packet or are unused. Upon a read request, the Payload is the data content of the selected configuration register. When initiating a Maintenance Response Packet, the hop count will be set to 0xFF.

The fields of the response packet are as follows:

- AckID = Transaction ID for link acknowledgements

- CRF = The incoming CRF is returned in the response

- prio = Increased to one higher than the request

- tt = Same as the request

- fType = Same as the request (8)

- ◆ Target ID = The Source ID of the request (a simple swap)

- Source ID = The Target ID of the request (a simple swap)

- transaction = specifies whether request is read, write and/or response, see sect 4.1.10 of sRIO Input/Output Logical spec

- status = 0000b means done, 0111b means error

#### **Notes**

- srcTID = the Transaction ID for sRIO end to end retransmissions (generated at the interface)

- ◆ Hop Count = Set to 0xFF to initiate the hop count

- Payload = 32 bits of data read from the designated register

- ◆ CRC = 16 bits of CRC

#### 3.4.10 Virtual Channel Handler

There is no virtual channel handler in the SerB. Virtual channels do not appear beyond the sRIO interface and have no affect on SerB operation.

## 3.5 sRIO Control Symbols

The sRIO control symbols are described in the sRIO Part 6: 1x/4x LP-Serial Physical Layer Specification in Chapter 3. Of particular note, these symbols are used to acknowledge all sRIO packets. The SerB shall support the following Stype 0 control symbols.

- Packet Accepted

- Packet Retry

- Packet Not Accepted

- Status

- Link Response

These control symbols shall be used to acknowledge all incoming sRIO packets and doorbells. Outgoing packets and doorbells shall expect a response and report errors when they occur.

# 3.6 Use of CRC and CRC Errors

The SerB shall have the capability of using CRC-16 and is defined in the sRIO "1x/4x LP-Serial Physical Layer Specification" in section 2.4.2.

The following rules dictate uses of CRC within the SerB:

- CRC will be CRC-16 with two bytes in size.

- CRC errors shall be counted. The counts shall be stored and readable through the configuration registers.

- If retransmission is turned off, a packet with CRC errors shall be dropped. There is no indication a bad packet was received. The CRC error will be logged. The user may use higher level detection to retransmit a section of data.

- All CRC errors will set the error flag and may cause interrupts or doorbells per the flag configuration.

- sRIO contains CRC in all packets. CRC suppression is used with the PPS.

- The minimum packet size when retransmit is turned on is 8 bytes payload.

### 3.7 Parallel Port Interface

The P-Port is a standard parallel interface that is used to drive QDRII SRAM devices. It has a 36-bit data bus, and other control signals that may be connected to a standard QDRII memory interface.

The SerB parallel port options:

- The SerB may act as a FIFO controller, using an external QDRII-B4 x36 memory as extra storage space that

may be allocated to the internal FIFO queue as desired.

- P-Port may be disabled, either by a pin, or by programming an internal register.

The definition of the P-Port interface in this specification is guidance only. The overriding requirement is that the SerB must connect to a QDRII-B4, x36 device.

### **Notes**

# 4.0 Data Handling Within the SerB

The S-Port on SerB has the ability to act as an sRIO Endpoint or as an sRIO Bus Master. When the SerB is outputting to an sRIO port, the queue holds the output packet routing information designating the final destination for the data.

In the PPS application, the SerB will typically act as an sRIO endpoint (slave), and will respond to commands received through the PPS. In the event that there is an active waterlevel = watermark, the SerB shall become the sRIO bus master to send the multicast packet to the PPS.

# 4.1 Inputting Data to the Queue

Incoming serial data must be directed to a queue upon entry into the SerB. The incoming packet data carries an identifier that selects a "case scenario" for the data that includes the routing information. In sRIO, the source ID of the data selects the "case scenario" for the data. This is designated at "Case Scenario Mode".

### 4.1.1 Command Input Buffer

There is an input buffer on the SerB that is capable of stacking a small number of commands. There is a separate buffer for read and write commands. It should be noted that commands may become blocked by activity within a queue in the SerB.

### 4.1.2 Output Buffer

There is an output buffer that is capable of stacking output packets on the SerB. In the event that multiple output packets become stacked within the buffer, the higher priority packets will be sent first. A packet that is blocked on the bus for any reason, will prevent the transmission of subsequent same priority packets and lower priority packets until the blocked packet successfully sends, or is discarded.

### 4.1.3 Writing More Data than can Accept

Whenever an attempt is made to write more data to queue than there is space available to accept, the SerB will go through the following stages:

- When the queue is full, a Full Flag will be set. The flag may then send any interrupts or doorbells to unmasked locations.

- The incoming data will be accepted in full packets and fill the input buffer on the FIFO port.

- If the input buffer contains data that it cannot flush into the queue, the data will sit there, preventing the port from writing to the queue. Priority and maintenance packets will not be blocked, but data packets will be blocked